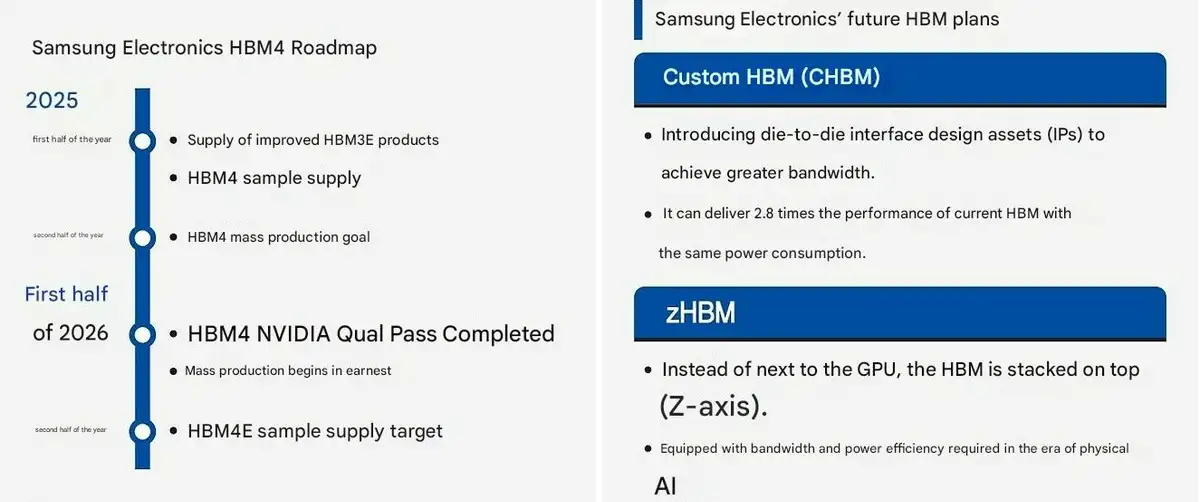

Samsung Electronics treibt die Entwicklung seiner Speicherlösungen der nächsten Generation voran. Im Fokus stehen dabei HBM4, das maßgeschneiderte cHBM und die vertikal gestapelte zHBM-Architektur. Song Jai-hyuk, CTO des Unternehmens, erklärte auf der SEMICON Korea 2026 in Seoul, dass die Produktionseffizienz von HBM4 ein hohes Niveau erreicht habe und das Kundenfeedback zur Leistung äußerst positiv ausfalle.

Serienproduktion von HBM4 startet

Samsung plant, noch in diesem Monat mit der Serienproduktion und Auslieferung der HBM4-Chips an Großkunden zu beginnen. Die Speicherlösung kombiniert zwei fortschrittliche Fertigungstechnologien: Die DRAM-Zellenschicht wird im 1c-Verfahren (Samsungs 10-Nanometer-DRAM der sechsten Generation) gefertigt, während der Basis-Die im hauseigenen 4-Nanometer-Foundry-Prozess entsteht.

Durch diese Kombination erreicht Samsung Datenraten von bis zu 11,7 Gigabit pro Sekunde (Gbps). Dieser Wert liegt deutlich über der JEDEC-Referenz von 8 Gbps. Laut dem CTO ist die aktuelle Fertigungsausbeute „sehr gut“ und die Kunden zeigen sich mit der Performance „äußerst zufrieden“.

cHBM: Ziel von 2,8-facher Energieeffizienz

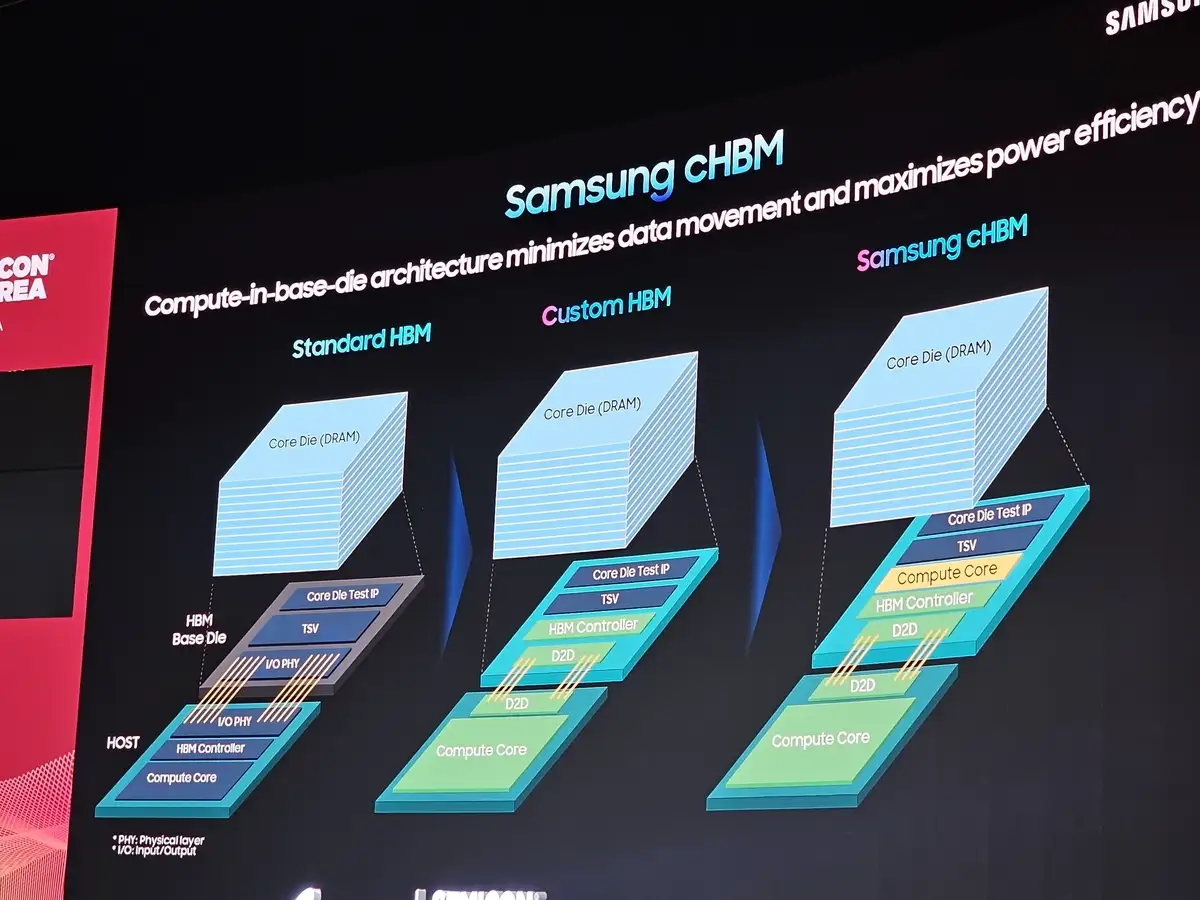

Wachsende KI-Workloads verändern die Speicherarchitektur von Beschleuniger-Chips. Samsung setzt hierbei auf Custom HBM (cHBM) basierend auf einer Compute-in-Base-Die-Architektur. Dabei werden Teile der Rechenlast, die normalerweise von GPUs übernommen werden, direkt in der Basisschicht des Speichers verarbeitet.

Diese Architektur soll die Energieeffizienz des Gesamtsystems um das bis zu 2,8-Fache steigern.

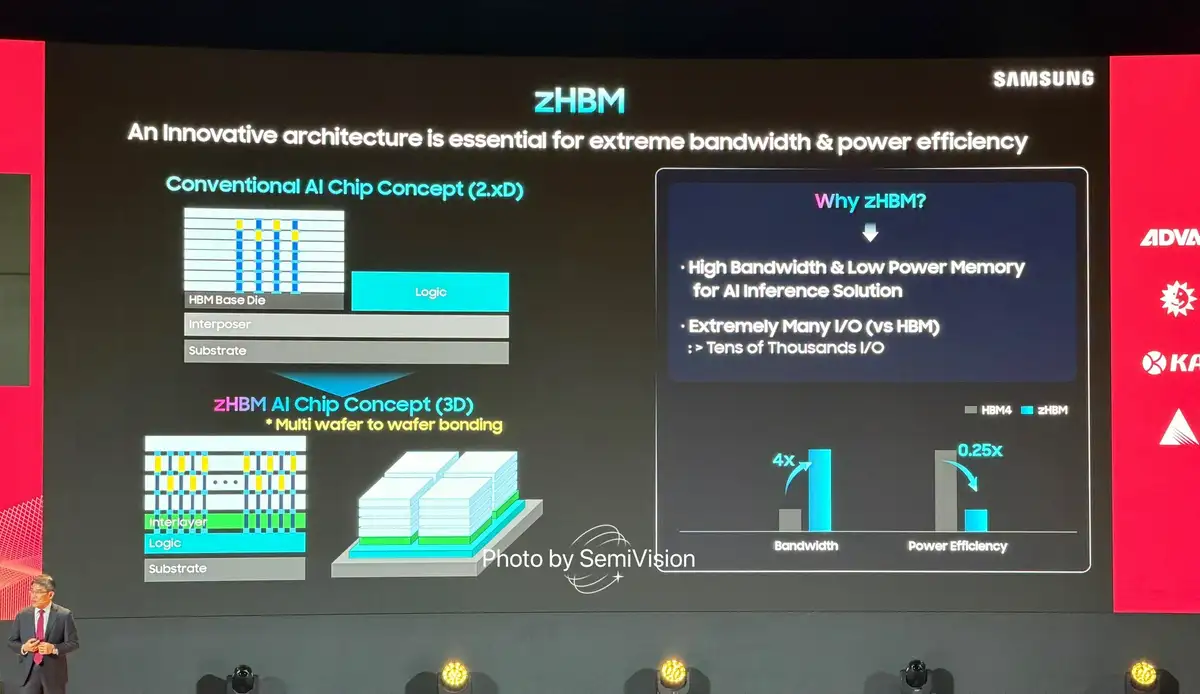

zHBM: 4-fache Bandbreite dank vertikalem Stacking

Eine weitere Neuerung ist zHBM. Hier werden die HBM-Schichten vertikal direkt auf die Logik-Chips gestapelt. Dies verkürzt die Signalwege und ermöglicht eine höhere Bandbreite bei geringerem Stromverbrauch.

Samsung prognostiziert für die zHBM-Architektur eine Vervierfachung der Bandbreite, während der Energieverbrauch um 25 Prozent sinkt. Dies markiert einen bedeutenden Sprung für Leistung und Effizienz.